Product Summary

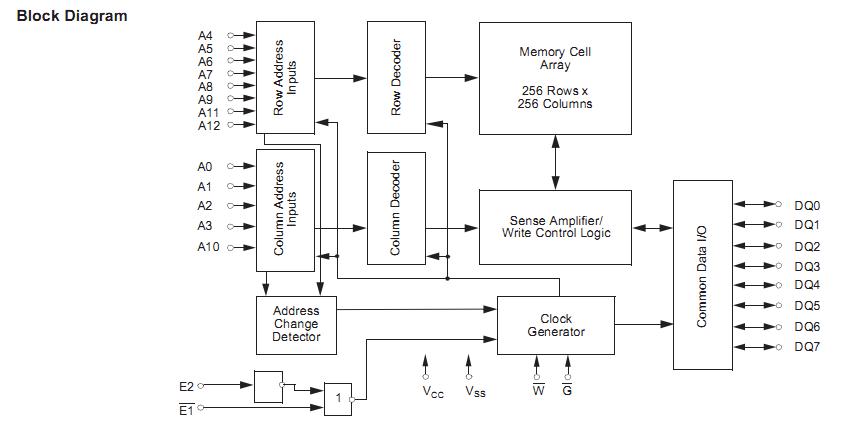

The U6264ADC is a static RAM manufactured using a CMOS process technology with the following ope-rating modes: Read, Standby, Write and Data Retention. The memory array is based on a 6-transistor cell. The U6264ADC is activated by the rising edge of E2 (at E1 = L), or the falling edge of E1 (at E2 = H). The address and control inputs open simultaneously. According to the information of W and G, the data inputs, or outputs, are active. During the active state (E1 = L and E2 = H), each address change leads to a new Read or Write cycle. In a Read cycle, the U6264ADC data outputs are activated by the falling edge of G, afterwards the data word read will be available at the outputs.

Parametrics

U6264ADC absolute maximum ratings: (1)Power Supply Voltage, VCC: 4.5 to 5.5 V; (2)Data Retention Voltage, VCC(DR): 2.0 V min; (3)Input Low Voltage, VIL: -0.3 to 0.8 V; (4)Input High Voltage, VIH: 2.2 to VCC + 0.3 V.

Features

U6264ADC features: (1)8192 x 8 bit static CMOS RAM; (2)70 and 100 ns Access Times; (3)Common data inputs and outputs; (4)Three-state outputs; (5)Typ. operating supply current: 70 ns: 45 mA; 100 ns: 37 mA; (6)Data retention current at 3 V: < 10 μA (standard); (7)Standby current standard < 30 μA; (8)Standby current low power (L) < 10 μA; (9)Standby current very low power (LL) < 1 μA; (10)Standby current for LL-version at 25℃ and 5 V: typ. 50 nA; (11)TTL/CMOS-compatible; (12)Automatic reduction of power dissipation in long Read or Write cycles; (13)Power supply voltage 5 V; (14)Operating temperature ranges: 0 to 70℃; (15)Quality assessment according to CECC 90000, CECC 90100 and CECC 90111; (16)ESD protection > 2000 V (MIL STD 883C M3015.7); (17)Latch-up immunity > 100 mA.

Diagrams

|

U6264BS2C07LLG1 |

Alliance Memory |

SRAM ZMD 8K x 8 5V Asynch |

Data Sheet |

|

|

||||||||||||

|

U6264BS2K07LLG1 |

Alliance Memory |

SRAM ZMD 8K x 8 5V Asynch |

Data Sheet |

|

|

||||||||||||

|

U6268B-MFPG3 |

|

IC INTERFACE DUAL SENSOR 16-SOIC |

Data Sheet |

Negotiable |

|

||||||||||||

|

U6264BDK07LLG1 |

Alliance Memory |

SRAM ZMD 8K x 8 5V Asynch |

Data Sheet |

|

|

||||||||||||

|

U6264BDC07LLG1 |

Alliance Memory |

SRAM ZMD 8K x 8 5V Asynch |

Data Sheet |

|

|

||||||||||||

|

U6264B |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))